1.1 Si功率器件

1.1.1 Si功率二极管

1.1.1.1 pn结

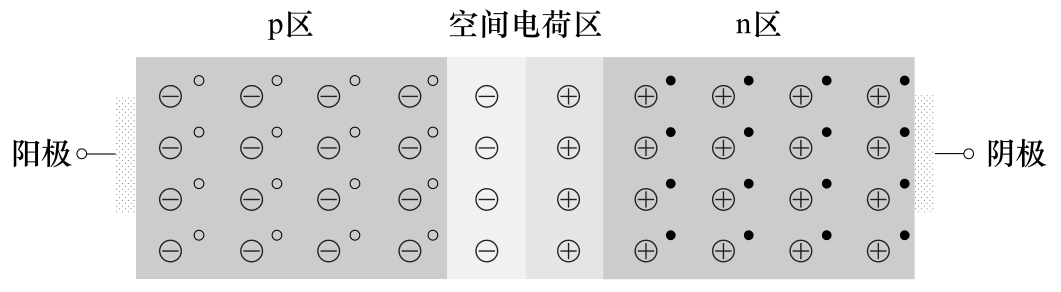

pn结是构成半导体器件的基本结构,是通过对p型半导体掺杂形成n区或者对n型半导体掺杂形成p区形成的,包含p区、n区和空间电荷区(耗尽层)三个部分,其结构如图1-1所示。

图1-1 pn结结构

以对p型半导体通过掺杂形成n区为例,由于存在较大的浓度差,p区的空穴(多子)会向n区扩散,n区的电子(多子)会向p区扩散。则在交界面附近,n区内掺杂的施主元素(通常为磷)由于失去电子而成为电离施主,带正电荷;p区内掺杂的受主元素(通常为硼)得到电子而成为电离受主,带负电荷。存在电离施主和电离受主的区域形成空间电荷区,进而形成内建电场,电场方向由电离施主指向电离受主,即由n区指向p区。

空穴和电子会在内建电场的作用下进行漂移运动,空穴朝p区漂移,电子朝n区漂移,漂移的方向与扩散的方向相反。当电子、空穴的扩散和漂移达到动态平衡时,空间电荷区宽度固定。当对pn结施加外加电场时,空间电荷区的宽度会发生变化:当在p区加正电压时,外加电场与内建电场方向相反,空穴漂移减弱,扩散相对加强,空间电荷区会变窄;同理,当在p区加负电压时,外加电场与内建电场方向相同,空穴漂移加强,扩散相对减弱,空间电荷区会变宽。

二极管最基本的结构就是上文所介绍的pn结,p区端为阳极、n区端为阴极。当在二极管两端施加反向电压时,pn结反向偏置,空间电荷区变宽并承担反向电压,扩散运动被大大削弱,漂移运动占主导地位从而形成反向漏电流,二极管处于阻断状态。当在二极管两端施加正向电压时,pn结正向偏置,p区电势升高;当所加正向电压大于空间电荷区内建电场产生的势垒电压后,扩散运动将占主导从而形成正向电流,此时二极管导通。

1.1.1.2 功率二极管种类与结构

1.pin二极管和快恢复二极管

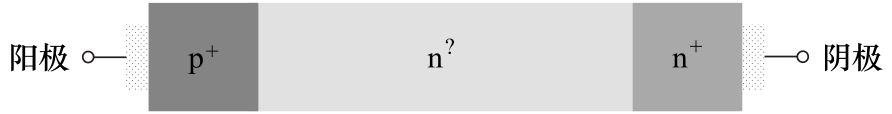

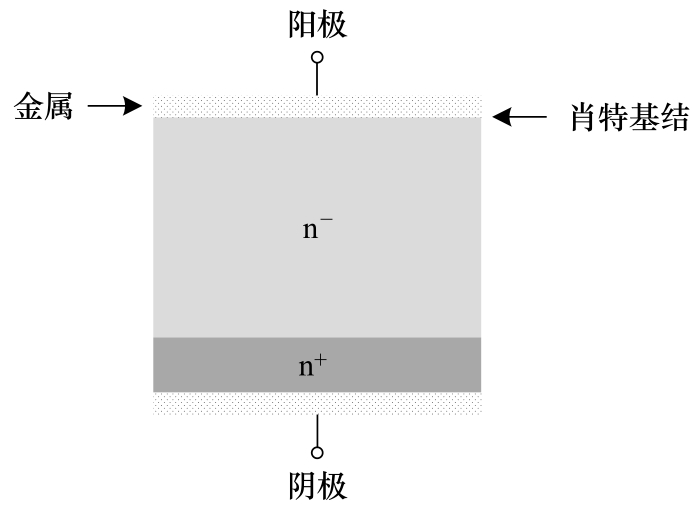

pn结二极管能够承受的反向电压较小,不适合作为功率二极管使用。为了提高其耐压值,在重掺杂的p + 区和n + 区之间增加一层较厚的低掺杂n - 型高阻区作为耐压层,成为pin二极管,如图1-2所示。由于耐压层掺杂浓度较低,相比高掺杂可看作是本征(intrinsic)状态,pin二极管因此得名。

当其承受反压时,p + -n - 结势垒升高,空间电荷区变宽且主要向低掺杂的n - 区展宽,由于掺杂浓度低、厚度宽,n - 区可以承受较高的反向电压。当对其施加正向电压时,p + -n - 结势垒降低,空间电荷区变窄,p + 区向n - 区注入空穴,n + 区向n - 区注入电子,在n - 区发生电导调制效应,从而在导通大电流时能够获得较小的导通压降。结合以上两点可知,pin二极管在关断时漏电流较小,能够在承受高反向电压的同时,具有良好的导通特性。

图1-2 pin二极管的结构

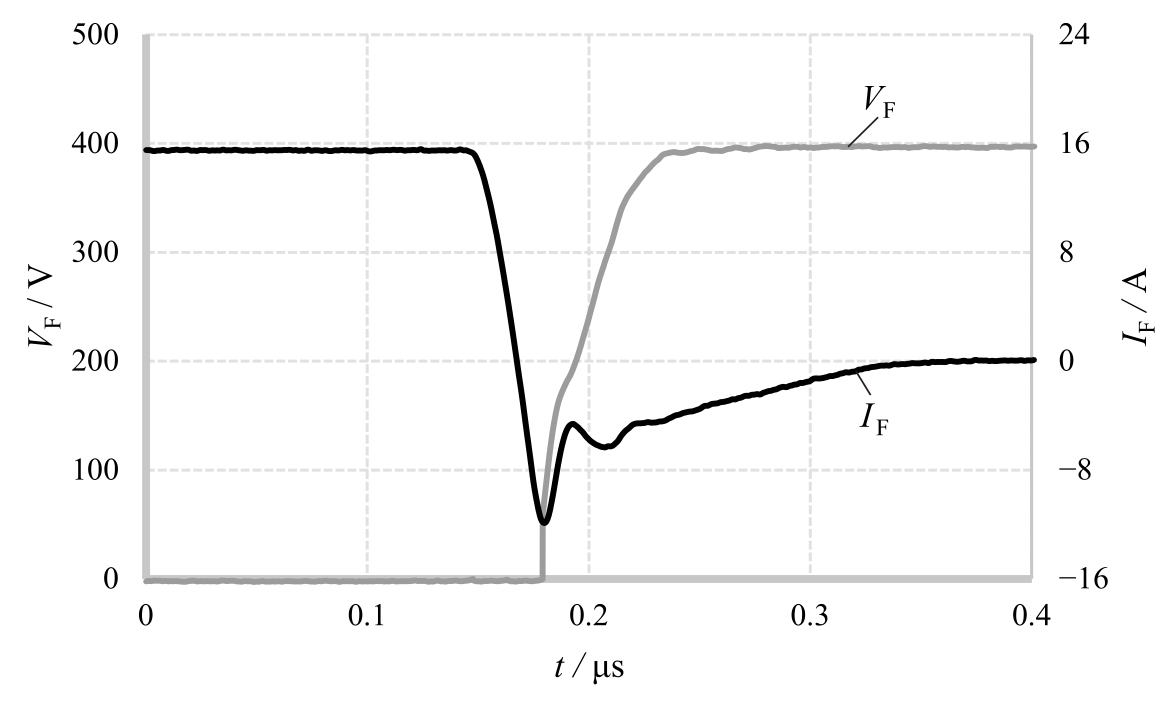

当对正向导通的二极管突然加反压时,二极管不会立刻关断,而是会经过反向恢复过程,如图1-3所示。二极管正向导通时,其正向电流是多子的扩散电流,n - 区充满电子和空穴。要将二极管关断就需要将n - 区的电子抽取回到n + 区、空穴抽取回到p + 区,这就使得在电流降至零后仍然有反向恢复电流存在。随着多子浓度不断降低,空间电荷区形成并不断展宽,反向恢复电流逐渐减小至零并承受反向电压,二极管关断完成。

由于pin二极管是双极型器件,导通时载流子浓度较高,不容易从较厚的n - 区中抽走,故其反向恢复时间较长。因此,pin二极管适用于中高压、对二极管反向恢复损耗不敏感的应用中,如用作整流二极管。

为了改善pin二极管的反向恢复特性,改变其阳极结构,从而控制阳极空穴注入效率、降低导通期间的少子注入,成为快恢复二极管,即FRD(Fast Recovery Diode)。

图1-3 二极管反向恢复过程

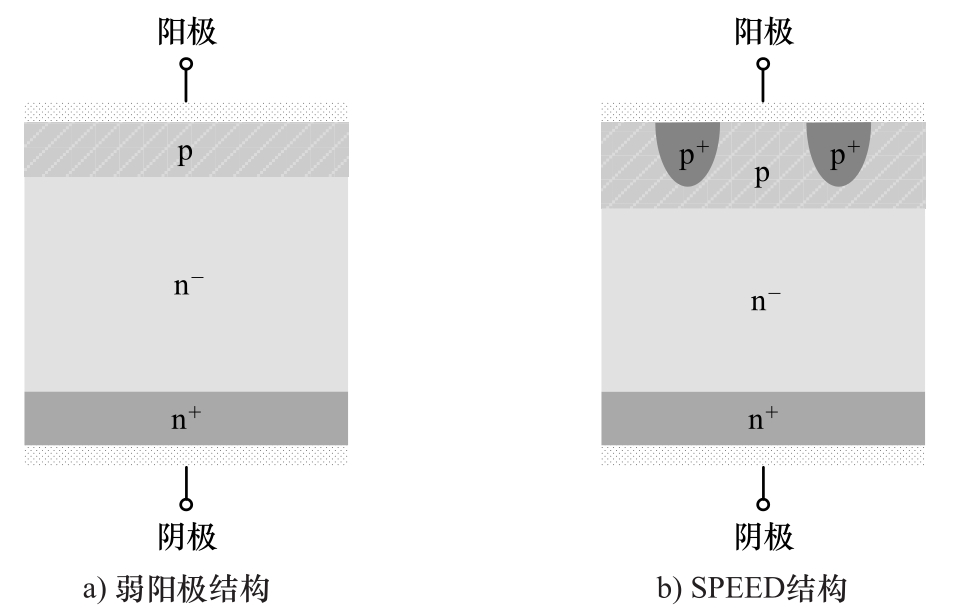

常见的快恢复二极管的结构有弱阳极结构和SPEED(Self-adjustable p + Emitter Efficiency Diode)结构,如图1-4所示。弱阳极结构是通过降低p区掺杂浓度来降低阳极注入效率,从而提高反向恢复速度。SPEED结构是将阳极改为在低掺杂p区中嵌入高掺杂p + 区,在导通电流较小时,由p区注入空穴,注入效率低,有利于提高反向恢复速度;在导通电流较大时,p + 区开始注入空穴,空穴注入效率高,有利于提高器件抗浪涌电流的能力。除了改变阳极结构之外,还可以通过质子辐照在阳极p + 区引入局部的复合中心来控制载流子寿命,以提高反向恢复速度,但这样做会显著增大漏电流。

图1-4 快恢复二极管结构

由于FRD的反向恢复时间短,具有较好的反向恢复特性,因此往往用作续流二极管。在实际应用中,除了要求反向恢复速度快,还需要恢复特性“软”,即反向恢复电流衰减平滑,不出现突然的、快速的跌落。这就需要改进二极管的阴极结构,来调整反向恢复末期的载流子浓度。

2.肖特基二极管

与传统基于pn结的二极管不同,肖特基二极管是通过金属-半导体结的势垒实现的,以其发明人Walter Schottky命名为SBD(Schottky Barrier Diode)。功率肖特基二极管包括普通功率肖特基二极管、结势垒控制的肖特基二极管、肖特基-pin复合二极管、超结-肖特基二极管。

(1)普通功率肖特基二极管

普通功率肖特基二极管是将pin二极管的p + 区换为金属作为阳极形成的,其结构如图1-5所示。肖特基二极管是单极型器件,只由电子导电,故开关速度更快、反向恢复特性更优。此外,肖特基结(金属-半导体结)的势垒高度比pn结的低,因此肖特基二极管的正向开启电压只有0.3V左右,比pn二极管的0.7V更低,故能大幅降低导通损耗。但同时也导致了其击穿电压低、漏电流大,因此适用于中低压应用场合。需要注意的是,尽管肖特基结的势垒高度低,但肖特基二极管是单极型器件,不存在电导调制效应,在导通电流较大时,漂移区正向压降仍会很高,这也限制了其在大电流场合的应用。

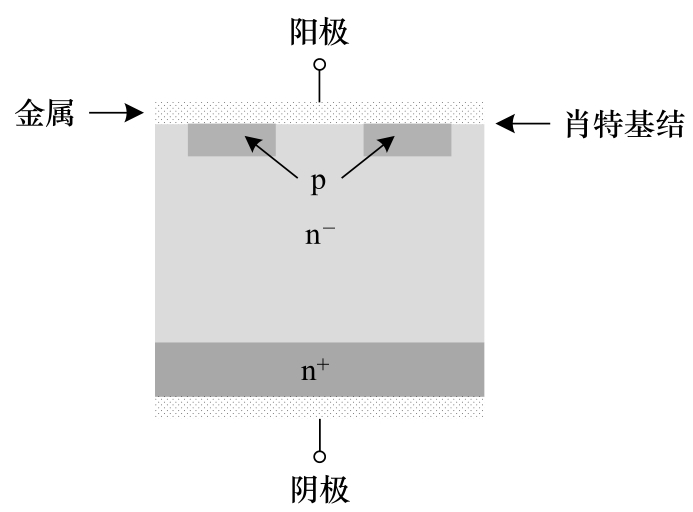

(2)结势垒控制的肖特基二极管

结势垒控制的肖特基二极管,即JBS二极管(Junction Barrier Schottky Diode),是在形成肖特基结之前,在n - 区上方间隔形成p区,p区与下方的n - 和n + 区形成pin二极管结构,因此可将JBS看作是普通肖特基二极管与pin二极管的并联,如图1-6所示。正向导通时,肖特基结势垒低,导通压降小;反向阻断时,间隔形成的p区与阳极金属组成JFET结构,在反向电压下,p区与n - 区形成的空间电荷区展宽,进而连在一起将肖特基结屏蔽起来,此时主要由pin二极管起作用,有利于阻断电压的提高。

图1-5 普通功率肖特基二极管结构

图1-6 结势垒控制的肖特基二极管结构

(3)肖特基-pin复合二极管

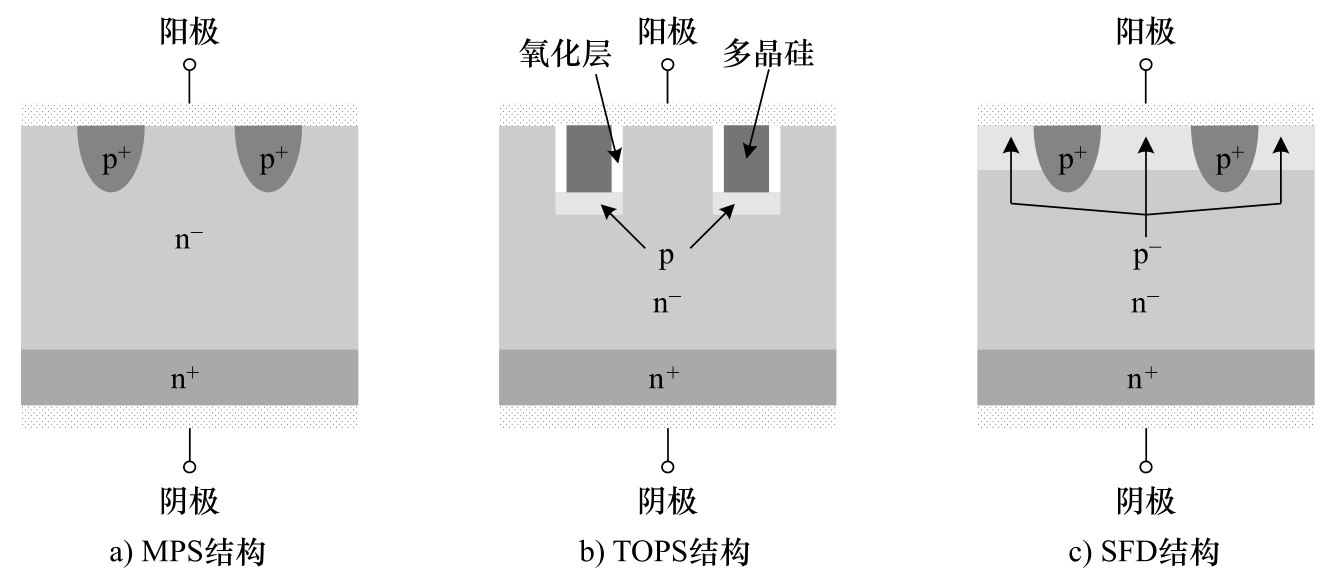

普通肖特基二极管和pin二极管分别具有快反向恢复和大功率、高耐压的特点,将两者结合发展出的肖特基-pin复合二极管兼顾两方面的优点,常见结构有MPS结构、TOPS结构和SFD结构,如图1-7所示。

图1-7 肖特基-pin复合二极管的结构

MPS(Merged PiN Schottky)结构与JBS类似,通过在普通SBD的n - 区生长若干p + 区,产生纵向的pin结构。MPS的p区结深相对JBS较深,导通电流较小时,pin二极管不导通;导通电流较大时,p + 区会向n - 区注入空穴,产生电导调制效应使得导通压降小。承受反向电压时,p + -n - 结空间电荷区会扩展,通过JFET效应将肖特基结屏蔽起来,从而提高击穿电压。

TOPS(Trench Oxide PiN Schottky)二极管通过先挖槽,离子注入形成p区,再依次填入多晶硅和二氧化硅的方式,使靠近阳极侧的空穴浓度进一步降低。

SFD(Stereotactic Field Diode)二极管通过使用Al-Si代替MPS的金属阳极,在p + 区之间形成一层薄薄的p - 区,以控制阳极注入效率,这样做在优化反向恢复特性的同时,提高器件耐压能力。

(4)超结-肖特基二极管

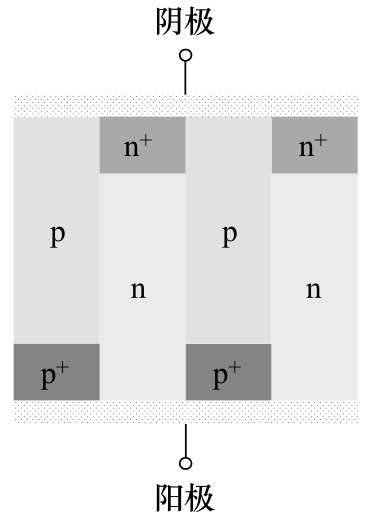

超结-肖特基二极管,即SJ-SBD(Super Junction Schottky Barrier Diode),其阳极和阴极均为金属电极,两极之间为相互平行间隔的p区和n区,对阳极附近p区和阴极附近n区进行重掺杂,与极板形成欧姆接触,轻掺杂区与极板形成肖特基结,如图1-8所示。在导通时通过纵向的肖特基结降低正向压降,在关断时通过超结结构形成横向电场,提高击穿电压、降低漏电流。

图1-8 超结-肖特基二极管

1.1.2 Si功率MOSFET

1.1.2.1 MOSFET基本原理

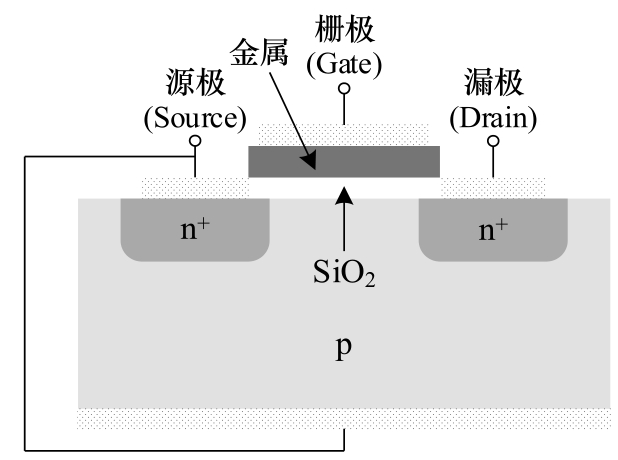

MOSFET是Metal-Oxide-Semiconductor Field-Effect Transistor的缩写,中文名为金属-氧化物-半导体场效应晶体管,是一种常用的单极型开关管。n沟道MOSFET的基本结构如图1-9所示,具有源极(Source)、漏极(Drain)和栅极(Gate)三端,并由栅极金属层(Metal)、作为绝缘材料的SiO 2 氧化物层(Oxide)和p型衬底半导体层(Semiconductor)形成了M-O-S结构。

当栅-源电压 V GS 为正时,栅极带正电荷,会在栅极下端的p区感应出带负电荷的反型层。当 V GS 足够高时,反型层将源极和漏极的n + 区连通,形成沟道。此时施加正向漏-源电压 V DS ,电子通过沟道流通,MOSFET导通。而当 V GS 不够高时,无法形成沟道,MOSFET关断,由反向偏置的pn结承受外加电压。

1.1.2.2 功率MOSFET种类与结构

1.横向双扩散MOSFET和垂直双扩散MOSFET

n沟道MOSFET的导通依赖于栅极下方p区反型后形成的沟道,关断时主要由漏极侧的pn结展宽承受电压。当将图1-9所示结构的MOSFET用作功率器件时存在矛盾:栅极下方p区长度不够时,MOSFET无法承受较高的反向电压,无法满足高压应用的要求;而当栅极下方p区长度过大时,沟道导通电阻过大,导致损耗增加,无法满足大电流应用的要求。

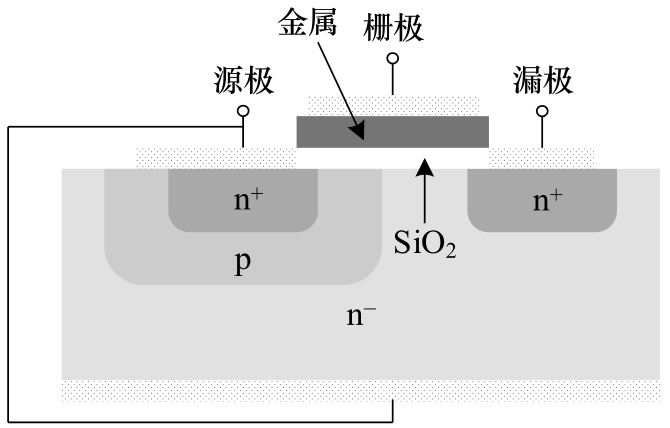

为了调和上述矛盾,在p区和漏极n + 区增加一个低掺杂的n - 区作为漂移区,成为横向双扩散MOSFET,即LDMOS(Laterally Double-Diffused Metal-Oxide Semiconductor),如图1-10所示。当LDMOS承受反向电压时,由于p区掺杂浓度远高于漂移区,因此耗尽区主要在漂移区扩展,阻断电压主要由漂移区的长度和掺杂浓度决定。此外,漂移区的电阻率低于沟道。则对于LDMOS,只需要增大漂移区的长度,就可以在提升阻断电压的同时使导通电阻相对增加得更少,实现了对阻断电压和导通电阻的折中。

图1-9 n沟道MOSFET结构

图1-10 n沟道LDMOS结构

为了提高耐压能力,就需要不断增大LDMOS漂移区的长度,从而导致漂移区导通电阻增大。同时,电流是在LDMOS表面是从漏极到源极横向流动的,而大部分衬底材料没有得到有效利用,占用芯片面积较大,不利于MOSFET的小型化。

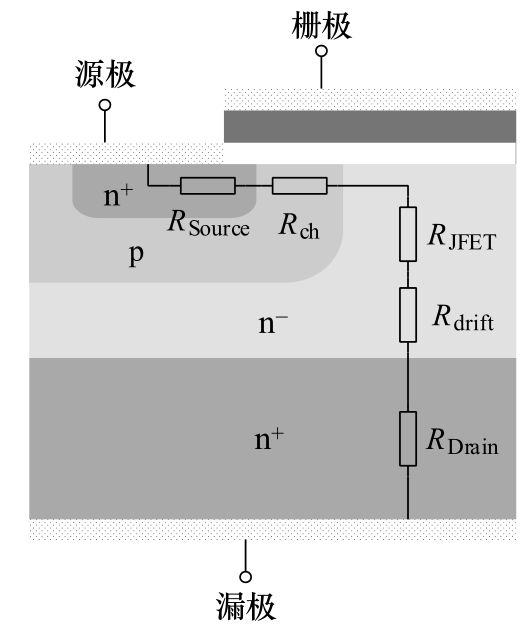

为了改善上述问题,将漏极移动到芯片的背面、与源极和栅极相对,成为垂直双扩散MOSFET,即VDMOS(Vertical Double-Diffused Metal-Oxide Semiconduc tor),如图1-11所示。在VDMOS中,电流垂直穿过MOSFET,最大限度地利用了漂移区,使其横截面积最大、沟道宽度最宽,从而显著降低了漂移区的导通电阻。VDMOS的阻断电压主要由漂移区的厚度决定,只需要增大漂移区厚度就可以提高阻断电压,不会影响芯片面积。另外,源极和漏极分别位于芯片的两面,轻松解决了高电压器件的绝缘问题。

按照电子流过VDMOS的顺序,其导通电阻 R DS(on) 依次包括:源极电阻 R Source 、沟道电阻 R ch 、电子离开DMOS元胞时JFET效应使元胞间电流通路变窄带来的电阻 R JFET 、漂移区电阻 R drift 和漏极电阻 R Drain ,如图1-12所示。

图1-11 n沟道VDMOS结构

图1-12 n沟道VDMOS导通电阻构成

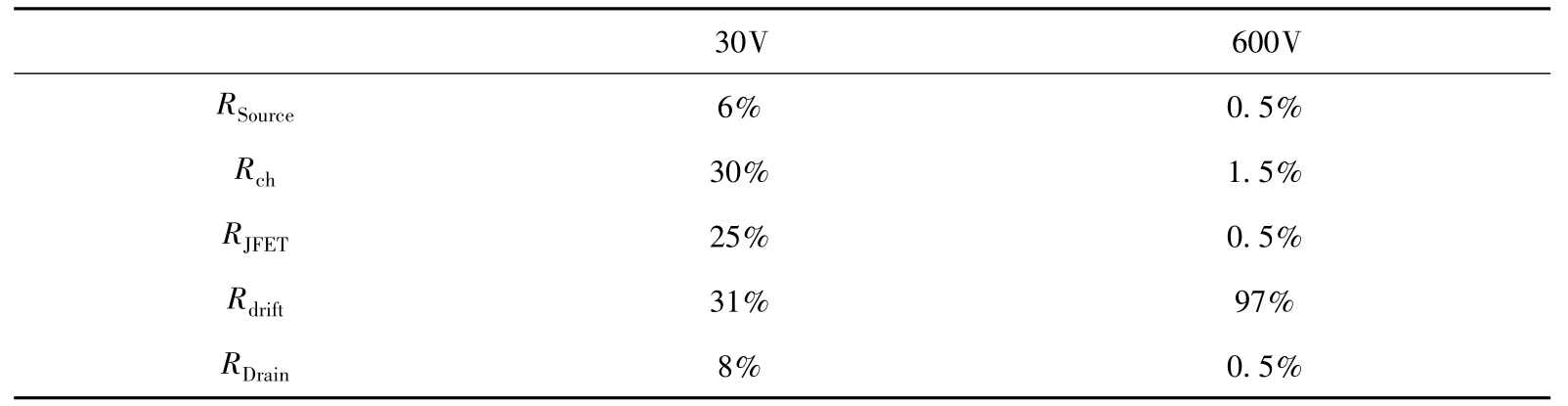

不同电压等级的VDMOS,其各部分导通电阻占总 R DS(on) 的比例见表1-1。低压VDMOS中, R ch 和 R JFET 占比较大;高压VDMOS中, R drift 占总 R DS(on) 中的绝大部分。为了降低 R DS(on) ,针对低压和高压器件,分别开发了沟槽技术和超级结技术,将在下文中详细介绍。

表1-1 VDMOS各部分导通电阻占比 [1]

2.沟槽栅MOSFET和屏蔽栅MOSFET

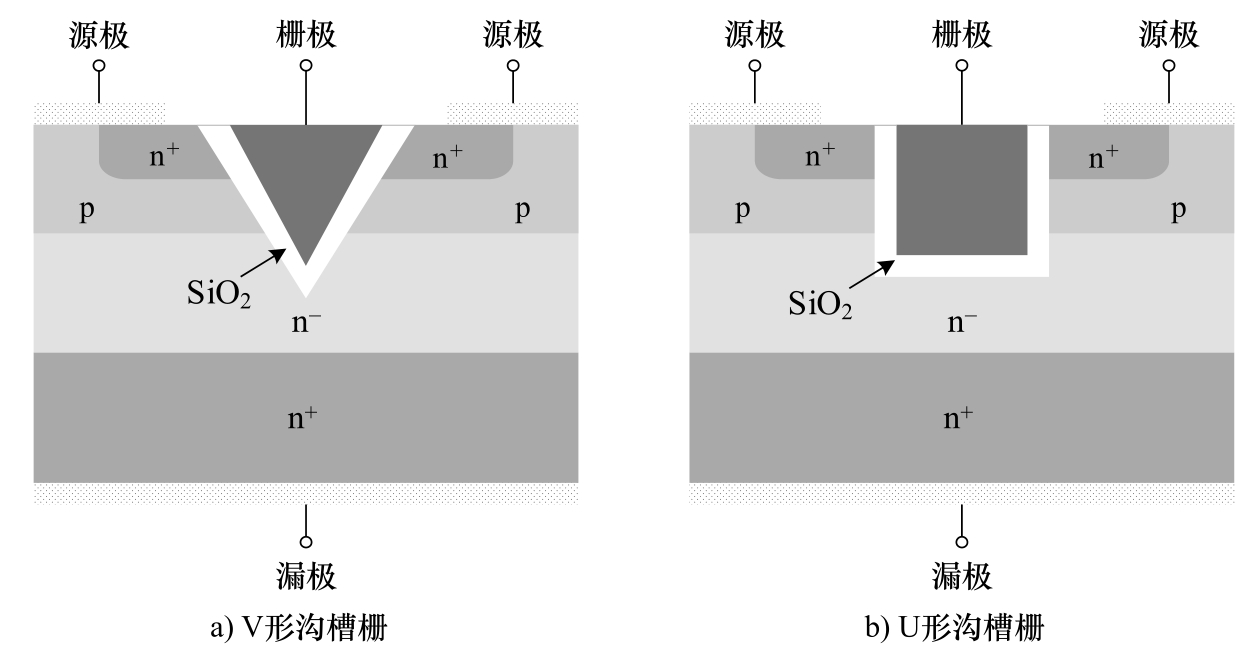

提高VDMOS的元胞密度可以降低 R ch ,但会使 R JFET 增大,两者存在矛盾。通过使用沟槽栅技术,将栅极结构从贴在芯片表面变为分隔在元胞间的沟槽,从而使沟道从水平方向转变为竖直方向,成为沟槽栅MOSFET,即Trench MOSFET,如图1-13所示,常见的沟槽栅有V形和U形。

VDMOS的JFET效应主要是由于元胞的pnp结构产生两个反偏的耗散层,同时n - 区浓度较低,因此耗散层较宽,限制了元胞间电流通路的截面积。沟槽栅结构避免了pnp结构的产生,竖直沟道的出口直接连接了开放的漂移区,JFET效应被完全消除。此外,相比水平方向,垂直方向沟道占用芯片面积很少,元胞密度可以进一步提高。则在相同的器件尺寸下,更多的元胞并联也会使 R drift 减小。

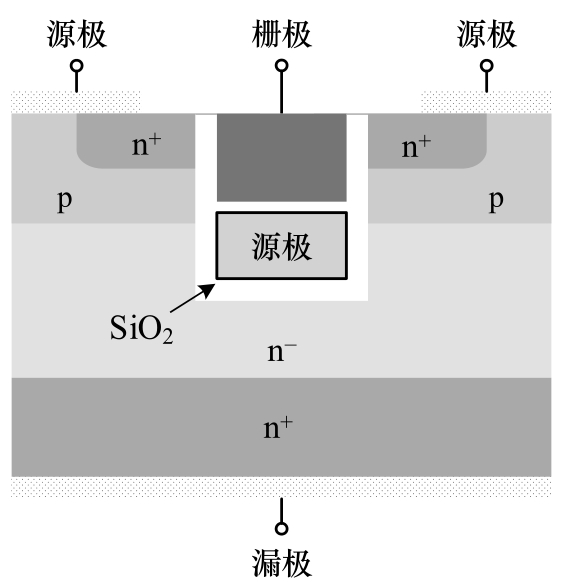

图1-13 n沟道沟槽栅MOSFET结构

当采用沟槽栅后,单个元胞的栅极与漂移区接触面积变大,同时元胞密度更高,这使得栅-漏电容 C GD 也随之变大,导致栅电荷 Q G 变大、驱动损耗增加、开关速度变慢。为了降低 C GD ,在沟槽栅中增加一层屏蔽栅,将下半部分的屏蔽栅与源极相连,成为屏蔽栅MOSFET,即SGT(Shielded Gate Trench)MOSFET,如图1-14所示。这就使得原本的 C GD 转换为栅-源电容 C GS 和漏-源电容 C DS , C GD 显著降低。

3.超级结MOSFET

高压VDMOS的 R DS(on) 主要由 R drift 决定,同时漂移区厚度决定阻断电压,其单位面积导通电阻 R DS(on),sp 与阻断电压的2.5次方成正比。 R DS(on),sp 随着阻断电压的升高而迅速增大,使得VDMOS无法同时满足高阻断电压和大电流,限制了其应用领域。

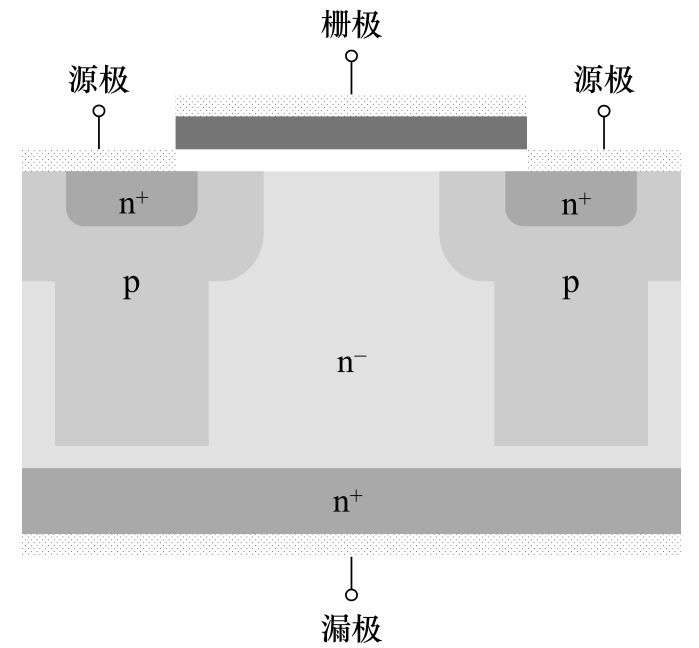

采用超级结技术,在VDMOS的基础上将p区向下垂直延伸,成为超级结MOSFET,即SJ-MOSFET(Super Junction MOSFET),如图1-15所示。在截止状态下,p柱和n - 柱形成横向pn结,产生横向耗尽,只要满足pn柱区的电荷平衡,就可以使空间电荷区横向展宽,将n - 区全部耗尽,形成一个近似矩形的电场,耐压能力得以提升。而在导通状态下,载流子从源极通过沟道进入超级结的n - 区,然后进入n + 衬底到达漏极。从上面的分析可以看出,在不影响耐压能力的前提下,提高n - 柱区的掺杂浓度即可显著降低漂移区电阻,进而显著降低导通电阻,使得其 R DS(on),sp 与阻断电压的1.4次方成正比。

图1-14 n沟道屏蔽栅MOSFET结构

图1-15 n沟道超级结MOSFET结构

1.1.3 Si IGBT

1.1.3.1 IGBT基本原理

MOSFET是单极型器件,通流能力相对较差,即使采用超级结技术,为了获得更大的通流能力,只能不断增大芯片面积,导致结电容过大,器件特性变差且通流能力有限。例如商用650V SJ-MOSFET的最低 R DS(on) 在20mΩ左右,电流等级在100A左右;800V SJ-MOSFET的最低 R DS(on) 在280mΩ左右,电流等级在17A左右。而IGBT为双极型器件,具有电导调制效应,能大幅度提升器件的通流能力。

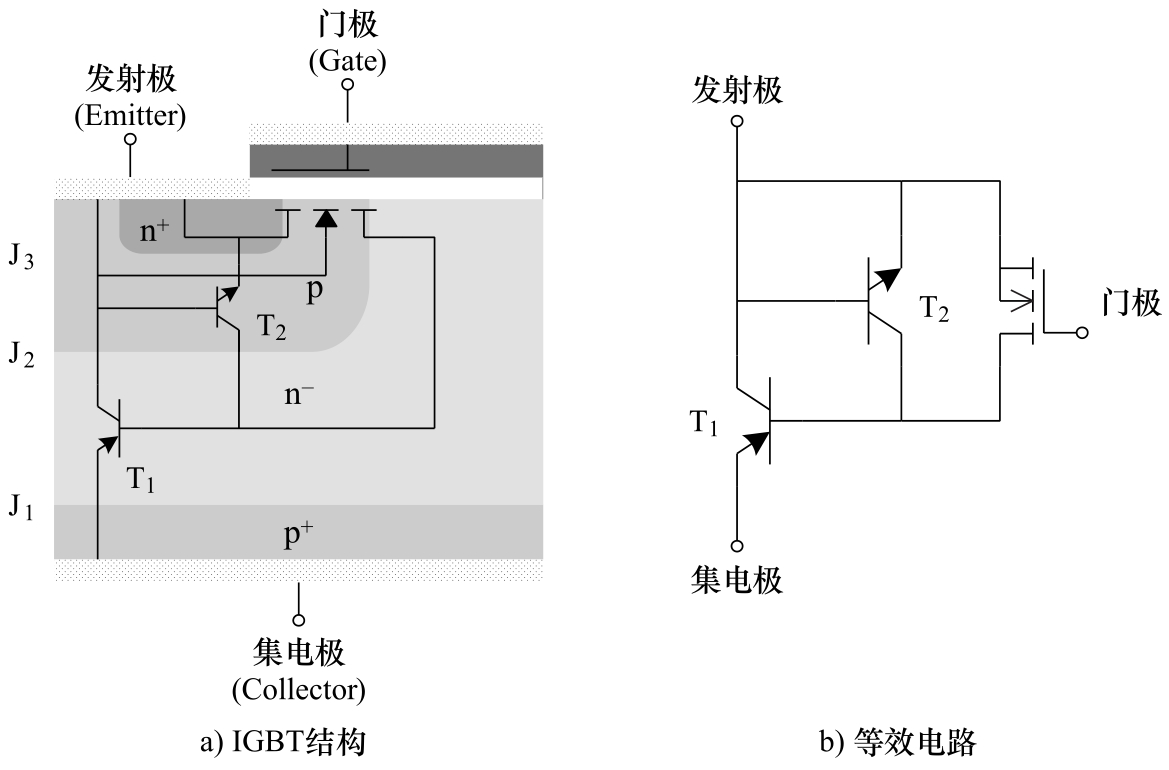

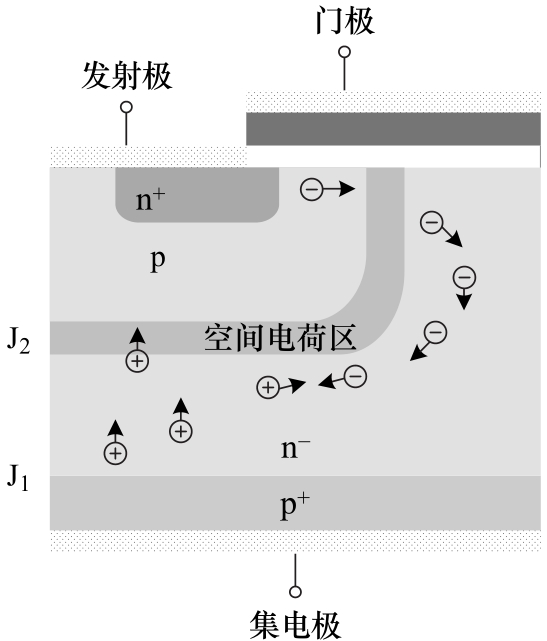

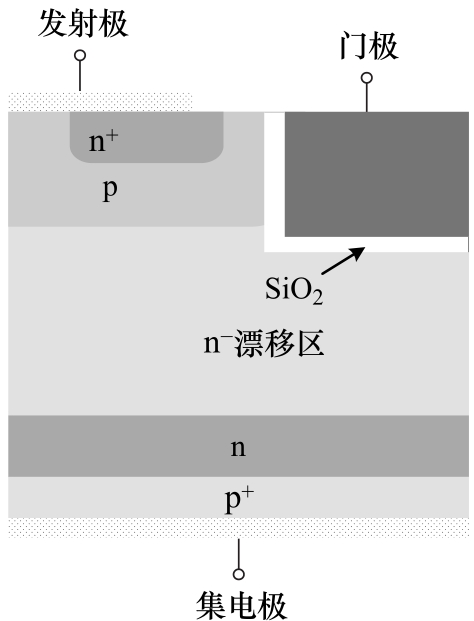

IGBT全称为绝缘栅双极型场效应晶体管,即Insulated Gate Bipolar Transistor,是将VDMOS中漏极的n + 层替换为p + 层构成的,如图1-16a所示,具有发射极(Emitter)、门极(Gate)和集电极(Collector)三极。IGBT拥有三个pn结:集电极p + 区与n - 区的pn结J 1 、n - 区与p基区pn结J 2 、p基区与发射极n + 区的pn结J 3 。故IGBT具有寄生pnp晶体管T 1 和npn晶体管T 2 ,同时还具有MOSFET结构,其等效电路如图1-16b所示。

图1-16 IGBT

IGBT工作原理如图1-17所示,当 V CE >0V时,J 1 正偏、J 2 反偏。当 V GE >0V时,感应出电子沟道,电子由射极n + 区流入n - 区,降低了n - 区电位,使得J 1 进一步正偏,p基区向n - 区注入大量空穴,其中一部分与射极n + 区流入的电子复合形成连续的沟道电子电流,另一部分由反偏的J 2 的电场扫入射极n + 区。而当 V GE ≤0V时,由于没有电子流入n - 区,无法为T 1 提供基极电流,IGBT处于正向阻断状态,由反向偏置的J 2 承担电压。故IGBT可以看作是由MOSFET控制的晶体管。

由于IGBT在导通期间n - 区积累了大量非平衡载流子,只有当它们完全复合消失后才会进入阻断状态,在关断过程中形成拖尾电流,导致其关断时间比MOSFET要长得多,限制了其开关频率一般在100kHz以下。此外,与VDMOS不同,当 V CE <0V时,寄生的pnp晶体管的发射结处于反偏,无法流过电流,故IGBT无法实现反向导通,在使用中需要额外使用反并联二极管。

1.1.3.2 IGBT种类与结构

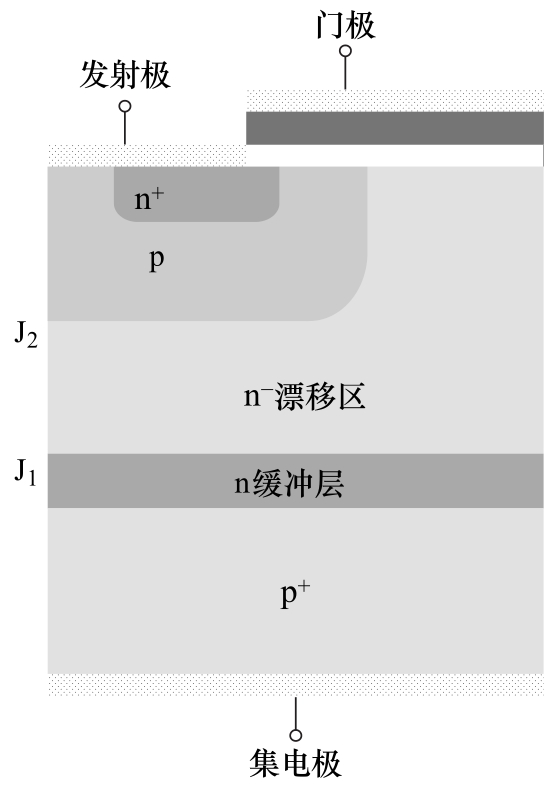

1.PT-IGBT与NPT-IGBT

最早的IGBT的纵向耐压结构是穿通型IGBT(PT-IGBT),如图1-18所示。当 V CE >0V,J 2 结反偏,耗尽层向n - 区扩展,穿通n - 区到n缓冲区,从而形成近似梯形的电场强度分布。由于p + 区较厚,且掺杂浓度较高,PT-IGBT的J 1 注入效率高、导通压降低,但是导通时在n - 区存有大量非平衡载流子,从而使得关断拖尾电流时间较长。一种比较直接的方法是引入载流子寿命控制技术,通过对器件关键区域进行高能电子辐照、重金属掺杂等方式,对材料的复合中心进行改善,控制载流子的寿命。尽管改进后关断特性有所改善,往往会引入器件参数漂移、特性退化、稳定性差等问题。

图1-17 IGBT工作原理

图1-18 PT-IGBT结构

除了上述导通压降和开关特性之间的矛盾,PT-IGBT还存在着通态压降在纵向分布不均的固有缺陷,且载流子寿命随温度升高而变长,器件呈负温度系数,不利于器件的并联使用。此外,这种IGBT是在较厚的p + 衬底上运用外延工艺制作上面的n - 区和MOS结构,成本较高。

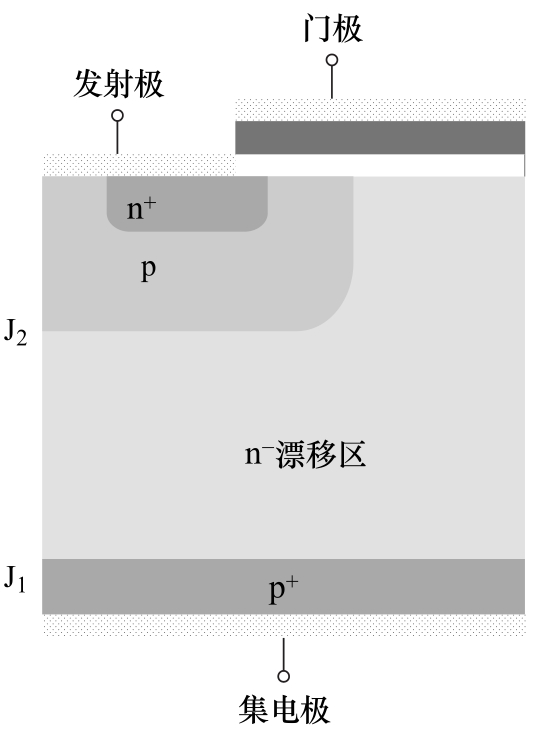

随着透明集电区技术的发展,如图1-19所示,非穿通型IGBT(NPT-IGBT)直接在低掺杂n型区熔硅单晶片上加工,集电极侧用离子注入形成p + 区。在J 2 反偏时耗尽层向n - 区扩展,由于n - 区较厚,当J 2 的峰值电场达到临界击穿电场时依然不会穿通n - 区,这就使得其电场分布为三角形,使通态压降在纵向分布更加均匀。用离子注入的方式生成p + 区,能降低J 1 结的空穴注入效率,减少拖尾时间。此外,NPT-IGBT的载流子寿命受温度影响小,而载流子迁移率的降低和接触电阻的增加明显,器件呈正温度系数,抗短路能力和抗动态雪崩能力很强,利于并联使用。但是NPT-IGBT有一个明显的缺陷,就是漂移区太厚,导致关断损耗较大。

图1-19 NPT-IGBT结构

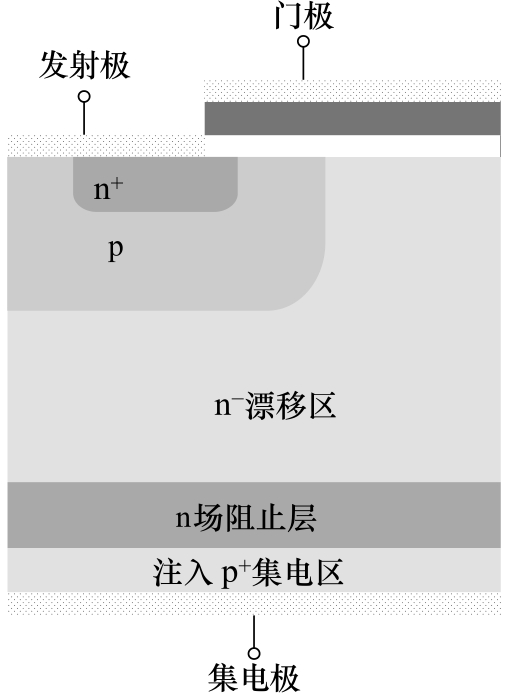

2.FS-IGBT

随着减薄工艺的发展,漂移区可以做得很薄,从而改善了导通压降的问题。但随之而来的另一个问题是,如何能在满足阻断耐压的同时,尽可能减小导通压降。场阻止型IGBT(FS-IGBT)能对此矛盾进行折中。

如图1-20所示,FS-IGBT在减薄技术、高能离子注入技术发展成熟的前提下,在晶圆背面通过离子注入形成一层几微米厚的场阻止层,其掺杂浓度相对PT-IGBT的缓冲层的浓度低一些,只对电场进行压缩,不阻碍空穴注入。这样,就可以形成类似PT-IGBT的梯形电场分布。集电极p + 区也采用透明集电极技术,即电子空穴注入效率相对较低,器件关断拖尾时间短。FS-IGBT温度特性和稳定性都与NPT-IGBT基本相同。此外,FS-IGBT的n - 区比NPT-IGBT更薄,导通压降更小,关断需要收取的载流子更少,关断损耗更小。在FS-IGBT的基础上,又出现了弱穿通(LPT)、软穿通(SPT)等IGBT。

3.沟槽栅IGBT

除了在纵向耐压结构上对IGBT进行改良,在横向方面,也将平面栅改成沟槽栅,如图1-21所示。与沟槽栅MOSFET相似,相比平面栅,沟槽栅使IGBT的沟道密度更大,表面利用效率更高,同时避免了JFET效应,减小了导通压降,增大了器件通流能力。但是沟槽栅结构也存在一些缺陷,会导致门极-集电极电容增加,影响其频率特性,限制高频的应用;同时,使IGBT的抗雪崩能力和抗短路能力降低。

图1-20 FS-IGBT结构

图1-21 沟槽栅IGBT结构