2.3 薄膜沉积

a-Si:H TFT制程中的薄膜从功能上包括导电薄膜、绝缘薄膜和半导体薄膜,其中后两种统称为功能薄膜。半导体薄膜是指沟道区的本征a-Si:H薄膜和欧姆接触的重掺杂n + a-Si:H薄膜。对a-Si:H薄膜的基本要求是低的缺陷态密度和低的界面态密度。在采用背沟道刻蚀型结构(BCE结构),沟道层的a-Si:H非常薄(约70nm),因此a-Si:H薄膜特性会受到临近薄膜特性的影响。为了获得优异的TFT特性,需要优化a-Si:H薄膜的沉积工艺,以便获得高质量、低缺陷态和界面态的薄膜。

2.3.1 概述

化学气相沉积是常用的薄膜沉积方法,根据激励源或沉积环境的不同,有常压CVD(APCVD)、低压CVD(LP CVD)、热CVD、光CVD、等离子体增强CVD(PECVD)、远程等离子体增强CVD(RPECVD)和电子回旋共振 CVD(ECRCVD)。薄膜沉积温度要低于现在普遍应用的无碱玻璃应变点温度(约650℃)以下。实践表明,PECVD是a-Si:H TFT制造中功能薄膜沉积的最佳方法。相比其他薄膜沉积方法,PECVD方法具有的优点如下。

● 可以制备多种性能优良的非化学计量比的绝缘薄膜和半导体薄膜;

● 可以在低温下沉积高质量的薄膜;

● 可以实现大面积、高均匀性薄膜的沉积;

● 可以高速率沉积薄膜。

一般说来,用PECVD制备的高性能的a-Si:H TFT具有的电学特性是约1.0cm 2 /V·s的场效应迁移率( µ eff )、小于2.5V的阈值电压( V th )、大于10 6 的电流开关比( I on / I off )和低的亚阈值摆幅(Sub-threshold Swing)。器件具备这些特性,与a-Si:H薄膜本体、接触界面等有着直接的关系。而这又受到PECVD沉积工艺条件的影响。比如,当沉积某一层薄膜时,之前沉积的或即将沉积的相邻薄膜的性质或界面特性可能受到当前薄膜沉积条件的影响。

2.3.2 a-Si:H薄膜的沉积

a-Si:H薄膜最主要的特点是非晶的、长程无序、内部含有大量的悬挂键。氢是钝化悬挂键最有效的介质。薄膜中氢含量受温度、功率和反应气体等工艺参数的影响。此外,a-Si:H 薄膜的其他特性:光敏感性、机械应力、界面粗糙度和局域态密度等,都与PECVD的沉积工艺条件有密切关系。

为了改善 a-Si:H 薄膜中氢的含量、薄膜的均匀性和形态,除了常用的 SiH 4 作为主要气源外,有时也用Si 2 H 6 和Si 3 H 8 为主要气源,并以H 2 、He或Ar等气体作为载气或稀释气体。

2.3.3 a-Si:H薄膜的影响因素

1.等离子体功率的影响

PECVD 的等离子体功率是薄膜沉积的一个最重要工艺参数,它直接影响着反应气体的分解效率、等离子中的电子能量和激子能量。研究发现,SiH 4 /H 2 或SiH 4 /He的等离子中a-Si:H沉积速率先是随着功率的增加而增加,到一定程度后(达到峰值),沉积速率将随着功率的增加反而下降。这主要是PECVD的等离子体环境中,薄膜沉积和刻蚀机理同时存在的缘故。SiH 4 和载气H 2 中的H激子,在薄膜沉积中,既起到钝化a-Si:H薄膜中悬挂键的作用,也起到刻蚀弱Si—Si键的作用。当刻蚀作用增强时,薄膜的沉积速率就会下降。

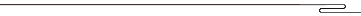

图2.6所示是等离子体功率对a-Si:H薄膜的自旋态密度、电导率和SiH 2 /SiH键的比例的影响。这些特性与薄膜的缺陷态密度或键结构有关。从图2.6 中可以看出,在较低功率范围内电导率随着功率的增加而降低,随后又随着功率的增加而略微增加。TFT的迁移率与a-Si:H薄膜的电导率有着密切关系;自旋态密度和SiH 2 /SiH比与薄膜中的缺陷态密度有关。除了a-Si:H薄膜自身的特性,沉积a-Si:H薄膜的功率也会影响到已经沉积了的绝缘层的界面性质。例如,高的a-Si:H薄膜沉积功率会引起下面栅绝缘层表面的损伤,引起薄膜表面粗糙和形成缺陷中心。这种损伤对迁移率形成负面效应。所以,在中等功率的沉积条件下,有利于获得高的迁移率。

图2.6 PECVD功率对a-Si:H薄

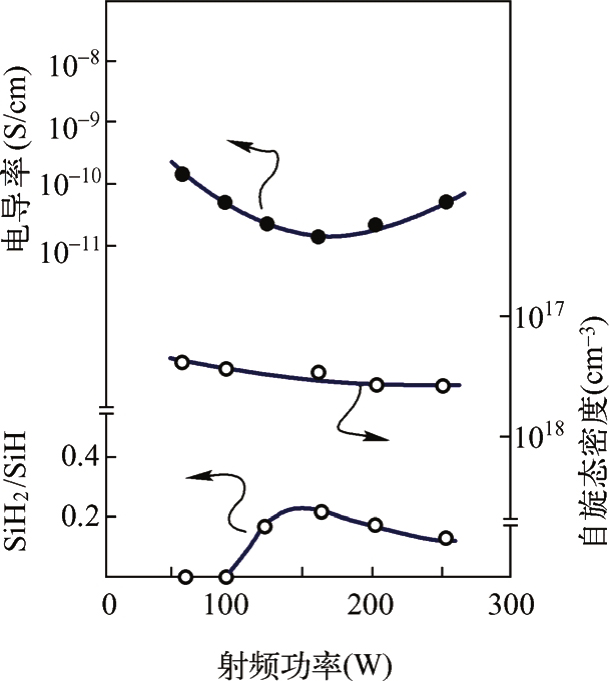

图2.7是底栅结构中不同等离子体功率下沉积的a-Si:H薄膜的TFT转移特性曲线。从图2.7中可以看出,相比较高的功率,在较低的功率下沉积的TFT具有较高的迁移率、较低的阈值电压和较高的亚阈值摆幅。高功率条件产生了高的氢浓度和高的等离子势能,增强了氢的刻蚀速率和表面功能基团,引起额外悬挂键的产生并导致下面栅绝缘层(SiN x )表面的粗糙,从而使TFT性能劣化。

图2.7 底栅结构中不同等离子体功率下沉

PECVD的等离子体频率也是影响TFT特性的另一个重要因素。PECVD常用的频率是13.56MHz,其他的频率,如50kHz、70MHz、144MHz或2.45GHz(ECR)也已经用于沉积a-Si:H薄膜。一般反应气体的分子分解效率和薄膜沉积速率随着频率的增加而增加。

调幅射频等离子体也可以被看成一种频率调整的方法。与传统的连续波形式等离子相比较,调幅射频等离子体在薄膜沉积中能产生更少的尘粒、更高的沉积速率,沉积薄膜的缺陷态密度也更低。

2.衬底温度的影响

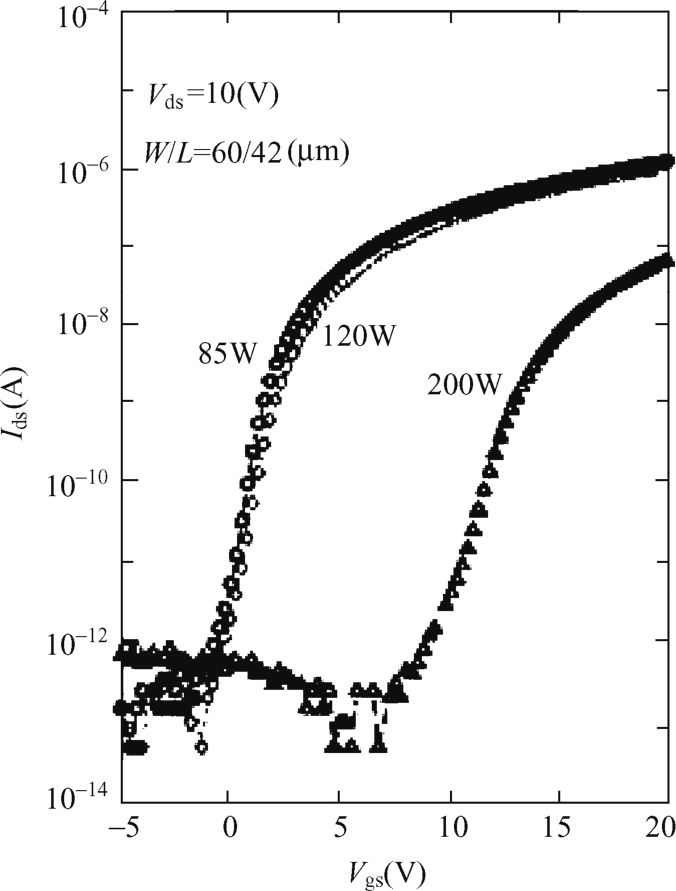

衬底温度不但影响着a-Si:H薄膜成膜的机理和反应速率,同时影响着其TFT器件的电学特性。图2.8是底栅TFT结构中,激活能和场效应迁移率随着衬底温度变化的关系曲线。从图2.8中可以看出,a-Si:H层在200~250℃的温度范围时沉积可以获得最高的器件迁移率。获得最高迁移率的衬底温度所对应的激活能(Δ E )最低。光声光谱仪(PSA)测量显示在这一温度范围沉积的 a-Si:H 薄膜带尾态密度非常低,这是产生高的TFT迁移率的主要原因。

图2.8 底栅TFT结构中,激活能和场效应迁移率随着衬

由于TFT是多膜层结构,因此仅仅给出优化的a-Si:H薄膜特性的沉积温度不一定能得到最好的TFT器件特性。这主要是各膜层工艺参数互相影响所致。a-Si:H薄膜的氢含量随着钝化层SiN x 沉积温度升高而降低。a-Si:H薄膜中氢的损失是由于热导致弱Si—H键破坏,H被释放出来或SiN x 沉积的等离子条件的影响。所以,为了获得最佳的TFT器件特性,在a-Si:H沉积温度被选取之后,其他薄膜的工艺参数都需要进行适当的调节。

3.a-Si:H薄膜的本体效应

在交叠和反交叠型的TFT结构中,源/漏电极和栅电极位于a-Si:H层的两边,所以,流经TFT的电流在垂直方向上两次经过a-Si:H薄膜本体材料。因此,a-Si:H薄膜本体材料的电学特性是不可忽略的。研究表明,a-Si:H 层的态密度越高(比如10 17 cm -3 eV -1 ),则通过它的压降就越高(比如高到5V)。此时,其TFT器件的 I-V 输出特性曲线上将出现非常严重的电流拥挤效应,即使源/漏区形成了良好的欧姆接触也是一样。a-Si:H 薄膜的态密度与它的悬挂键密度有密切关系,悬挂键有正、负和中性三种带电状态。形成悬挂键的主要原因是未钝化的硅原子。因此,用H钝化这些悬挂键,可以降低态密度。这也是为什么沉积a-Si:H薄膜时要求高氢浓度的原因。

在多膜层结构中,a-Si:H本体态密度低于a-Si:H/栅绝缘层界面处的态密度。由于绝大多数TFT的特性都受这一界面特性的影响,因此在a-Si:H沉积开始对界面态进行控制是非常关键的。采用两步a-Si:H沉积法可以有效控制a-Si:H/栅绝缘层的界面,同时不损伤薄膜本体的特性。a-Si:H/栅绝缘层界面态也与栅绝缘层本身的特性有关。a-Si:H 薄膜本体中的氢会受其后的钝化层的沉积条件而改变。所以,评价TFT中的a-Si:H薄膜的本体效应,必须考虑全部的制程工艺条件。

研究表明a-Si:H薄膜本体厚度也影响TFT的特性。一定TFT W / L 比值下,一般随着a-Si:H层厚度的降低,TFT的关态漏电流( I off )和光敏性会下降,但是阈值电压( V th )会增加。同样厚度的a-Si:H薄膜, W / L 越大, I off 也越大。当a-Si:H薄膜极薄时,初始沉积的a-Si:H薄膜可能是不连续的,这将导致低的TFT器件迁移率。

当a-Si:H薄膜厚度增加时,TFT器件发生以下变化:

● 亚阈值摆幅增加;

● 表面场效应迁移率下降;

● 阈值电压下降;

● γ 系数下降。

厚的a-Si:H薄膜的TFT器件表面场效应迁移率下降可能是由于寄生串联电阻增加所导致的。a-Si:H薄膜厚度增加导致的阈值电压下降,可能是由于背沟道界面的影响更弱所导致。a-Si:H薄膜厚度的增加而导致的 γ (反映带尾态密度)指数的下降,暗示了在更厚的a-Si:H薄膜中导带带尾态密度更低。更厚的a-Si:H薄膜制备的TFT,其电学性能比更薄的要更好(具有更高的场效应迁移率和更低的阈值电压)。这主要是随着a-Si:H薄膜厚度的增加,薄膜质量得到了改善。但是,需要注意的是,a-Si:H薄膜更厚时TFT器件的电流拥挤现象会更明显,源/漏串联电阻也增加。因此有必要在a-Si:H半导体的质量和其电阻值之间找到一个最佳匹配值。

4.a-Si:H薄膜的光电导效应

a-Si:H是众所周知的光电导材料,即它的电导率在可见光的照射下会急剧增加,这是由于光子能量使载流子从非导电态激发到导电态的缘故。而且,当对TFT器件施加栅电压的情况下,能带弯曲使光电导效应增强。

由于a-Si:H的这一光电导特征,导致在光照TFT特性下 I off 增加和 V th 降低。降低a-Si:H TFT的光电导效应的方法有以下几种:

● 用金属和/或黑色聚合物等不透明的薄膜材料沉积在TFT的上端和下端,以分别遮挡入射的背光源光和环境光。

● 如前面所述,减薄a-Si:H薄膜厚度可以降低光电导。这是因为a-Si:H的光电导正比于光吸收效率,薄膜越厚,光吸收效率越高,产生的电子-空穴对越多。但是a-Si:H薄膜厚度受器件结构的影响。如果是底栅背沟道刻蚀型结构(BCE),则在刻蚀沟道的掺杂层(n + a-Si:H薄膜)时,此时它和本征层的刻蚀选择比小,因此a-Si:H需要有较厚的厚度;而在刻蚀阻挡层型结构(ESL),在刻蚀沟道的n + a-Si:H薄膜时,此时掺杂层与SiN x 层的刻蚀选择比大,因此本征的a-Si:H可以很薄。相比,ESL的器件结构的光致漏电流比BCE的要低。

● 研究发现在a-Si:H本体材料的带隙中引入复合中心可以减少光致漏电流。复合中心的引入可以调整a-Si:H薄膜的沉积工艺条件,如SiH 4 /Ar比例、等离子体功率、衬底温度和反应压力等条件来实现。但是,薄膜缺陷又使TFT器件性能劣化而无实用性。

5.a-Si:H薄膜迁移率的提高

在AMLCD中,a-Si:H TFT具有更高的迁移率,意味着TFT的响应速度更快,能获得更高的显示帧速或像素透过率。文献报道的a-Si:H TFT典型的最大迁移率约1.0cm 2 /V·s。但是在大规模量产中,既需要获得大的载流子迁移率,同时也要确保迁移率具有重复性和稳定性,以确保产品性能的稳定。因此,面板厂业内工艺能力稳定达到的迁移率一般是约0.75cm 2 /V·s。

迁移率的提高,关系到TFT中电流通道的各个电阻。电流从源极到漏极的总电阻是由下列电阻串联而成的。

(1)源/漏极的金属与掺杂层的接触电阻;

(2)电流穿过源/漏极的掺杂层的电阻;

(3)源/漏极掺杂层与本征a-Si:H层的接触电阻;

(4)电流垂直穿过非载流子积累的本征a-Si:H层电阻;

(5)穿过载流子积累区(沟道)的电阻。

降低上述电流通道中电阻的任何工艺都可以提高迁移率。采用的工艺措施通常如下。

(1)反应气体中掺入合适比例的H 2 来降低a-Si:H薄膜中的缺陷;

(2)降低与a-Si:H薄膜接触的栅绝缘层界面的粗糙度的工艺,以及避免接触界面受污染的工艺(在同一真空环境中连续沉积薄膜);

(3)降低a-Si:H薄膜层的厚度,或a-Si:H薄膜的分层沉积。

等离子体功率适当增加可以提高载流子的迁移率,改善原因可能是薄膜缺陷更多地被氢钝化。如果功率太高,迁移率又降低,可能原因是高等离子能量造成了薄膜损伤。

提高TFT器件迁移率的根本方法是把非晶硅转化为微晶硅或多晶硅的形式。为了获得高电导率的 μc-Si:H 薄膜,输入氢气的浓度必须在 95%~96%之上,以提高氢的刻蚀能力。但是在AMLCD中,如何在低的工艺温度、大面积处理能力和高产量上制备微晶硅和多晶硅是需要权衡的。

2.3.4 n+a-Si:H薄膜的沉积

金属薄膜与半导体的a-Si:H薄膜直接接触将产生肖特基势垒而劣化TFT器件的电学特性。因为a-Si:H薄膜是弱n型半导体材料,因此它是一种n型沟道的器件,源/漏电极接触区用磷(PH 3 )实现电子重掺杂,形成n + a-Si:H薄膜,即掺杂层。如果用硼(B 2 H 6 )掺杂,可以形成p型a-Si:H TFT,但是其场效应迁移率比n型的要差很多。

采用大规模集成电路制程工艺中的离子注入实现重掺杂,对于AMLCD是不可取的,主要是离子注入工艺需要对注入源进行高温退火激活步骤,而且掺杂效率低,高掺杂浓度需要长的注入时间。a-Si:H TFT中最普遍的掺杂方法就是使用PECVD直接沉积PH 3 掺杂(与H 2 浓度比例是1%)的n + a-Si:H薄膜,磷的浓度在1020 cm -3 以上。

沉积n + a-Si:H薄膜,最普通的混合气体为SiH 4 、H 2 和PH 3 。有时也用其他的含硅气体,如SiH 2 Cl 2 或SiF 4 来代替SiH 4 。杂质浓度、杂质激活的效率、缺陷状态及形貌等因素会影响掺杂薄膜的电导率。这些特征又取决于薄膜沉积参数,如气体成分、氢的浓度、等离子功率、反应压力和衬底温度等。衬底的温度影响沉积速率和薄膜的电导率。随着温度的升高,薄膜沉积速率和电阻率都降低。由于温度的升高使成膜基团在衬底表面的附着系数减小,所以随着温度的升高沉积速率降低。此外,与低温沉积的薄膜相比,高温沉积的薄膜致密且氢的含量低。这主要是高温下表面反应速率高,反应生成物更接近于化学剂量比,所以高温沉积的薄膜致密且氢的含量低。恰当的工艺条件,可以得到低掺杂的μc-Si:H薄膜,它比高掺杂的a-Si:H薄膜具有更高的电导率。

为了获得源/漏电极与半导体之间的欧姆接触,需要沉积高电导率的n + a-Si:H薄膜,而且该薄膜与本征的a-Si:H薄膜间的接触电阻也要非常低。高电导率的n + a-Si:H 薄膜的电阻率在100Ω·cm左右,比本征a-Si:H的低7个数量级。如果制备成n + μc-Si:H薄膜,电阻率可以降低到1Ω·cm左右。

2.3.5 绝缘层薄膜的沉积

以a-Si:H为半导体层的TFT器件中,绝缘层一般都采用SiN x 薄膜。在器件中一般是两层SiN x ,一层作栅绝缘层,常写作g-SiN x ,另外一层作钝化层,常写作PVX(Passivation)。在以氧化物(IGZO)为半导体的TFT器件中,一般会用到SiO x 绝缘层。

a-Si:H薄膜上下表面都覆盖着绝缘薄膜,因此其性质和沉积工艺直接影响着TFT器件的各种特性。栅绝缘层主要影响TFT器件的关态漏电流和开态漏电流,钝化层主要影响关态漏电流。a-Si:H/栅绝缘层SiN x 界面处的固定电荷可使栅绝缘层和a-Si:H界面处的能带弯曲,影响TFT器件的电学特性,在a-Si:H层非常薄时,这种界面影响更为显著。

表征绝缘薄膜的物理参数主要有介电常数、应力、热稳定性、组分和键能等,它们影响着绝缘层的电学性能:电荷陷阱密度、平带移动和击穿电压。而绝缘层的这些电学性能又与 TFT 器件的电学性能息息相关,如场效应迁移率、阈值电压、电流开关比和亚阈值摆幅等。对于大面积的绝缘薄膜沉积,还需要考察的特征参数是沉积速率、厚度均匀性、刻蚀坡度角、针孔(Pinhole)密度等。

1.绝缘层薄膜的沉积方法

与a-Si:H薄膜的沉积方法一样,在AMLCD中,为了匹配a-Si:H薄膜的低温沉积工艺,绝缘层也需要使用低温的方法进行沉积。这些沉积方法有低压CVD、常压CVD、远程等离子CVD、光CVD、PECVD、溅射、蒸镀、金属阳极氧化和旋涂等。蒸镀和旋涂方法被认为是有机绝缘层(苯基环丁烷BCB)涂布的最佳工艺。早期用钽(Ta)作金属电极,因此在栅电极图形完成后,对Ta金属进行阳极氧化形成绝缘性的Ta 2 O 5 ,起到增强栅绝缘层的作用。

实践表面,与沉积a-Si:H薄膜的方法一样,PECVD方法被认为是沉积绝缘层SiN x 最理想的方法,具有面积大、均匀性高、产量高和电学性能好的特点。而且采用真空腔连续生长方式,可以在不暴露空气环境中进行多层薄膜的连续沉积,确保各层薄膜之间界面特性相互匹配。

2.SiN x 薄膜的沉积工艺

如前所述,常用PECVD 射频频率13.56MHz来沉积SiN x 薄膜,也可使用其他频率,如40MHz、60MHz和电子回旋共振2.45GHz来沉积SiN x 。薄膜的沉积也是采用多腔室系统来进行,避免薄膜的非连续沉积造成界面污染。PECVD SiN x 薄膜沉积常用的气体是SiH 4 和NH 3 ,并掺入一定比例的N 2 或H 2 ,有时也掺入某种惰性气体如氦气以调节薄膜特性或者均匀性。

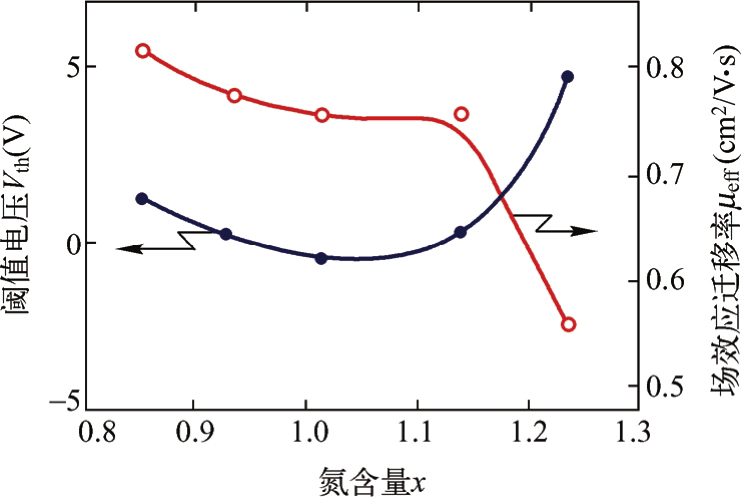

应用于a-Si:H TFT栅绝缘层的PECVD方法沉积的SiN x 薄膜应是稍富氮且含大量的氢(20%以上)的薄膜。图2.9所示是底栅结构TFT器件阈值电压和场效应迁移率对栅绝缘层SiN x 膜里氮含量( x )的依赖关系。N/Si比例,即SiN x 中的 x ,由Auger来确定。从图2.9中可以看出,当 x >1.1后,阈值电压随着 x 的增加而增加,迁移率随着 x 的增加而降低。因此,为了获得高的迁移率,同时低的阈值电压, x 值应该选合适的数值。偏压应力试验结果和SiN x 薄膜的光致发光光谱分析表明具有最小阈值电压漂移和最低缺陷态密度的 TFT 器件所对应的 x ≈1。PECVD沉积的SiN x 通常包含SiH和NH 基团,它们捕获不同类型的电荷。当薄膜的折射系数在1.85~1.90,薄膜内可能具有SiH和NH基团的优化组合,获得的薄膜本体内具有低的缺陷态密度和低的电荷陷阱中心、最小的a-Si:H/SiN x 界面态密度。a-Si:H和栅绝缘层SiN x 间的应力匹配或许是获得低的阈值电压的另外一个重要因素。因此,为了获得最好的TFT 器件特性和可靠性,栅绝缘层SiN x 要稍微富氮,具有低的压应力和高的光学带隙。

图2.9 底栅结构TFF器件阈值电压和场效应迁移率对栅绝缘层SiN x 膜里氮含量( x )的依赖关系

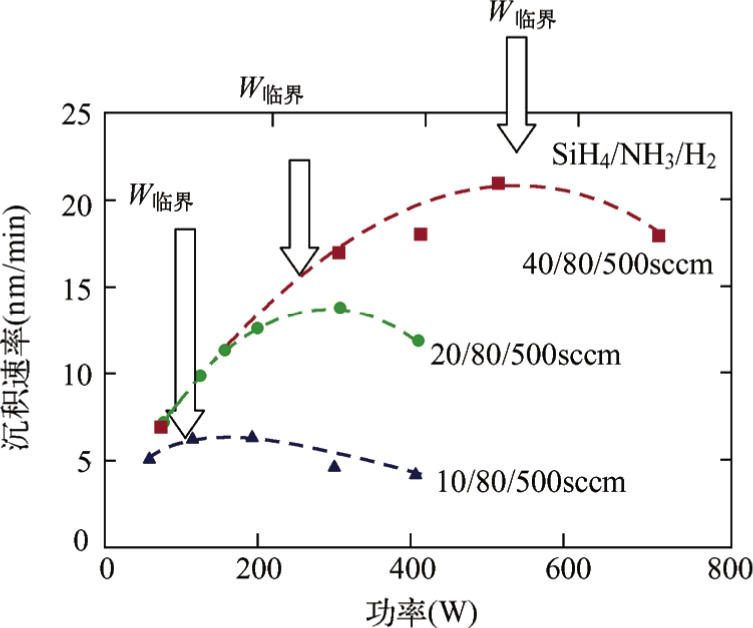

等离子功率是氮化硅薄膜沉积工艺的一个重要参数。图 2.10 所示是在不同的SiH 4 /NH 3 /N 2 气体流量比,500mTorr和250℃条件下等离子体功率与薄膜沉积速率之间的变化关系曲线。对于每一条曲线都有一个临界功率值( W 临界 )。小于临界功率值时,沉积速率随着功率的增加而增加,大于临界功率时则随着功率的增加而减小。使用不同的气体如SiH 4 、NH 3 、N 2 及H 2 也可以看到类似的变化关系。临界功率值随着硅烷浓度的增加而增加,这个现象可以用沉积和刻蚀同时发生的机理加以解释。

图2.10 不同比例的输入气体(SiH 4 /NH 3 /N 2 )时SiN x 薄膜的沉积速率与等离子体功率的变化关系

输入气体的分子(SiH 4 、NH 3 及N 2 )分解成薄膜的中间产物,分解的效率随功率的增加而增加。当功率较低时,中间产物在衬底表面上的吸附和反应生长占据优势,即薄膜沉积速率快;当功率大于某个值时,氢激子及高的离子轰击能量表现的刻蚀机理作用最大。此外,等离子体功率也影响薄膜的折射率、SiH/NH成分比和键的变化、薄膜应力和大面积沉积薄膜的厚度均匀性等。Auger 结果显示Si/N比例随功率的增加而增加,这一点恰好与薄膜的光学带隙的变化相一致,即随输入气流中氢浓度的降低或等离子功率的增加,薄膜的光学带隙增加。

当等离子体功率增加时,薄膜的应力由张应力变到压应力。最小的应力对应于临界功率附近。薄膜中氮的浓度与应力相关,具有高氮含量的SiN x 薄膜呈张应力,而低氮时则呈压应力。SiN x 薄膜厚度的均匀性在高功率下会变得劣化,直到接近临界功率附近。可能原因是随着功率的增加沉积工艺中氢的刻蚀机理作用更加明显,导致反应均匀性变差。高的等离子体功率也会促进等离子相内颗粒成核速率加快,这些颗粒吸附在沉积的薄膜上,造成薄膜电学特性变坏。因此,在薄膜沉积工艺中限制等离子功率低于临界功率可能减少等离子体内颗粒的产生。

氢是SiN x 薄膜中的重要组成部分,它可以钝化悬挂键从而可以降低缺陷态密度。通常氢由等离子体中的NH 3 或SiH 4 分子分解得到,也可以在输入气体中通入一定比例的H 2 ,以改变薄膜的键结构和沉积速率。研究表明,SiN x 薄膜中Si—H键随着输入气体中H 2 含量的增加而明显增加,而其他氢键(例如N—H或SiH 2 )的浓度会减少。高的H 2 浓度降低了薄膜的沉积速率或许是由于刻蚀机理的原因。

2.3.6 薄膜的界面效应

1.界面粗糙度和应力的影响

界面的粗糙度是由两种薄膜的沉积条件所决定的,其粗糙度直接影响TFT器件的性能。通常低的等离子体功率能获得更平滑的薄膜表面,其TFT器件的迁移率更高、阈值电压更低。

在较高等离子体功率下,在 SiN x 薄膜上面沉积 a-Si:H 时获得的界面更粗糙。因为高功率a-Si:H沉积条件的等离子体中通常具有高的氢的浓度和高的等离子体电势。这两个因素增强了 SiN x 表面上不同功能基团的选择性刻蚀,从而使得表面粗糙和缺陷增多。具有平滑的低缺陷a-Si:H/SiN x 界面的TFT器件特性比粗糙的多缺陷的要稳定得多。在a-Si:H比较薄的情况下,器件性能对界面特性更敏感。

由于界面特性的影响,沟道中a-Si:H薄膜的性质整体上是不均匀的。邻近的SiN x 层成分和结构会影响这层薄a-Si:H的特性。当SiN x 为富氮时,意味着a-Si:H界面薄层处的深局域态增加。深局域态增加可能产生大的应力失配。一般 a-Si:H薄膜具有压应力,而SiN x 薄膜根据氮含量或折射率系数可以表现为张应力或压应力。当SiN x 薄膜极大程度地富氮或富硅时都会导致界面处薄膜间的应力失配。高的应力失配引起低的迁移率和高的阈值电压。

2.界面特性的改善

因为氢具有钝化悬挂键的作用,并且稍微富氮的 SiN x 具有更优良的电学特性,因此a-Si:H/SiN x 界面特性的改善依赖于向界面处引入额外的氢和/或氮来钝化悬挂键或产生富氮的绝缘层SiN x 。

对于底栅TFT,由于栅绝缘层SiN x 沉积是在a-Si:H沉积之前,因此改善界面的措施是在沉积a-Si:H薄膜之前将SiN x 薄膜表面用NH 3 、N 2 、H 2 或O 2 的等离子体处理表面。研究结果表明,用这种方式改善效果有限。当表面用氢等离子体处理时,迁移率虽然提高了,但是关态漏电流也会增加。当表面用NH 3 等离子体处理时,TFT器件性能中除了耐正偏压应力特性外其他全部劣化。这样的结果主要是由于等离子体中的氢扮演着多重角色,既钝化了悬挂键,又有选择地将某些基团从薄膜表面移除,导致薄膜表面变得粗糙并产生气体悬挂键。用N 2 等离子体也可以改善SiO 2 栅绝缘层表面,获得更高的迁移率。界面特性改善后,迁移率提高,阈值电压降低。在等离子的氢化、氧化或氮化过程中,处理时间或功率变化范围通常不大。因为时间过长或功率过大,将破坏栅绝缘薄膜的内部。例如,在等离子体中的短波长光将穿透栅绝缘层薄膜而产生新的悬挂键。该现象在a-Si:H TFT的等离子刻蚀中也是众所周知的。

在栅绝缘层SiN x 薄膜沉积中,通常采用双层栅绝缘薄膜沉积,通过不同的沉积工艺来改善与a-Si:H接触界面的特性。也就是一层SiN x 当作界面层,一层当作本体层。界面层和本体层可能有许多不同的特性,比如耐刻蚀性和应力。虽然本体层可以采取非SiN x 的绝缘材料,但是在大规模量产中,通常两层绝缘薄膜都使用SiN x 。沉积这两层薄膜时,可以在同一腔室内进行,只需要适当调节工艺参数,如等离子体功率、气体流量比和反应压力等,就能获得性质有差异的薄膜,如改变氮含量。同时,厚的体绝缘膜可以高速沉积,而薄的界面层可以低速沉积以获得良好的界面特性。

除了a-Si:H和栅绝缘层之间的界面,a-Si:H层另一侧的界面即背沟道也是影响薄膜晶体管的重要因数。在沉积钝化层之前,BCE结构的TFT背沟道区经过刻蚀工艺受到严重损坏或污染,而ESL结构的TFT背沟道就获得了很好的保护。BCE结构中受到的损坏或污染,主要是在背沟道刻蚀中,腐蚀性的刻蚀剂不但破坏了a-Si:H的化学结构,引起大量悬挂键和缺陷的产生,同时造成表面粗糙、吸附刻蚀剂并残留。因此,在沉积背沟道的钝化层薄膜之前,需要用不同类型的等离子来改善a-Si:H的上表面以减小态密度,从而改善TFT性能。

现在的TFT器件结构,已经普遍采用底栅的结构。底栅与顶栅结构相比,最大的差异是薄膜之间的沉积顺序不同,由此造成了TFT器件有很大的差异。相比底栅结构,顶栅结构的界面具有较大的界面态密度,这可能与薄膜的沉积条件有关。与a-Si:H薄膜沉积条件相比,SiN x 等离子体功率更大,等离子体中的氢浓度高,由此对于顶栅结构在栅绝缘层SiN x 沉积过程中a-Si:H表面将受到损坏,造成表面形成大量的悬挂键。同时,顶栅中栅绝缘层的氢含量也更高,导致带隙加宽。因此,在不同的器件结构中,a-Si:H 与SiN x 薄膜的沉积顺序对界面特性有很大的影响。