2.5 TFT器件结构与特点

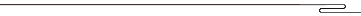

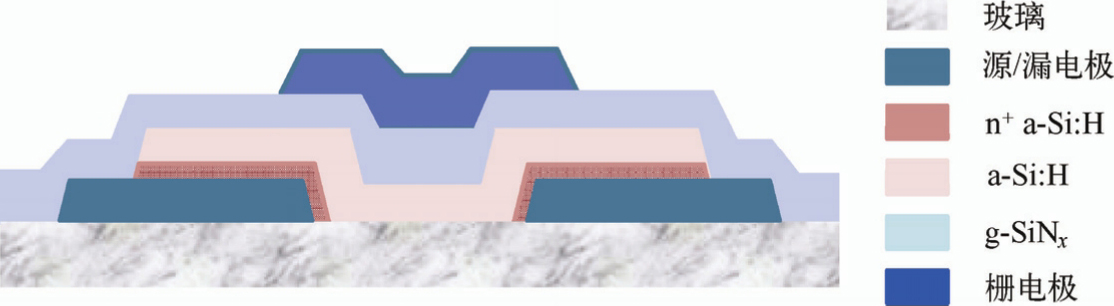

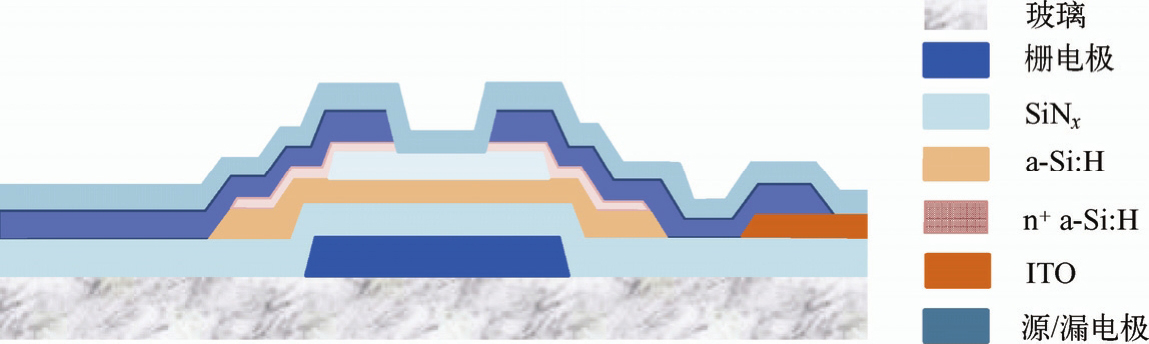

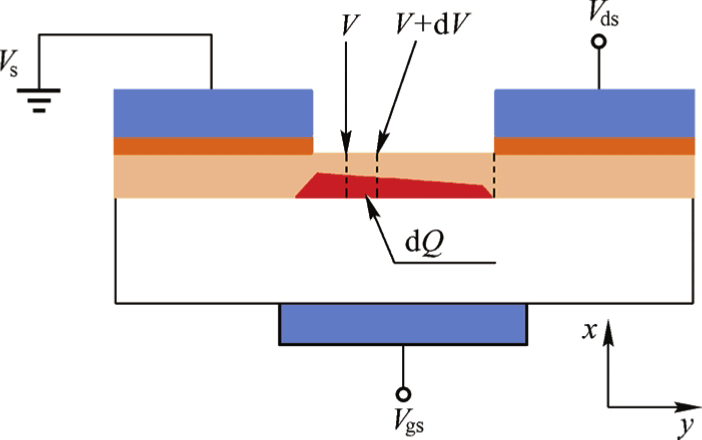

薄膜晶体管的基本组成包括两层金属(常用 Al 或 Cu)、两层绝缘层(一般是SiN x :H)、一层有源层(一般是a-Si:H)和一层位于半导体与金属层之间的欧姆接触层(n + a-Si:H)。两层金属构成的电极分别是扫描信号金属电极和数据信号金属电极;两层绝缘层分别指位于有源层下方的绝缘层(业内通常称为栅绝缘层,写为 g-SiN x )和位于有源层上方的绝缘层(业内通常称为钝化层,写为 PVX);有源层和欧姆接触作用的掺杂层一起在薄膜晶体管中通常是个岛状图形,因此有时又被称为有源岛或硅岛。如图2.11和图2.12所示,根据栅电极与硅岛的上下位置关系,薄膜晶体管的结构可以分为底栅结构和顶栅结构,其中底栅结构又被称为反交叠型结构(Inverted Staggered Structure),顶栅结构又被称为交叠型结构(Staggered Structure)。

图2.11 顶栅TFT结构

图2.12 底栅TFT结构

2.5.1 底栅结构

目前的液晶显示器广泛采用的是底栅结构。因为液晶显示是被动发光器件,即显示屏背面需要一个背光源,在底栅结构中不透光的栅电极金属层能很好地把来自背光源的光遮挡住,避免光线照射到硅岛上产生光生载流子而影响薄膜晶体管的关态电流特性。

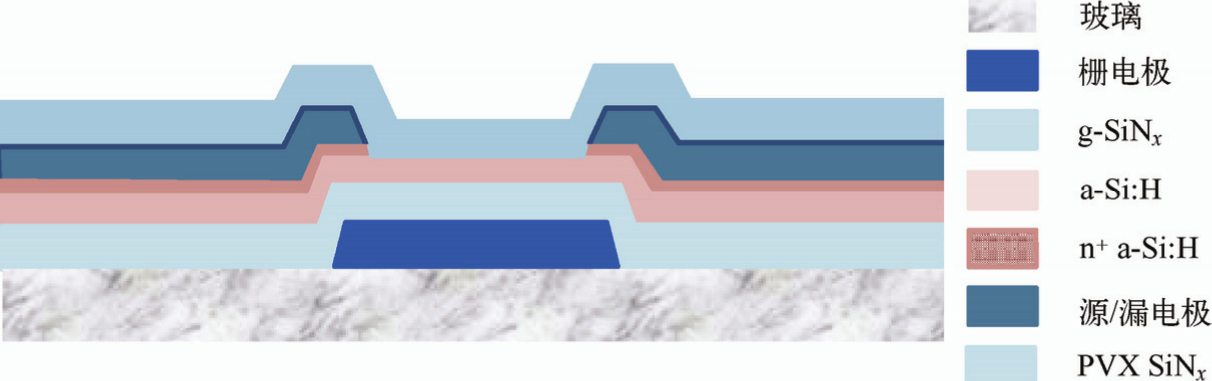

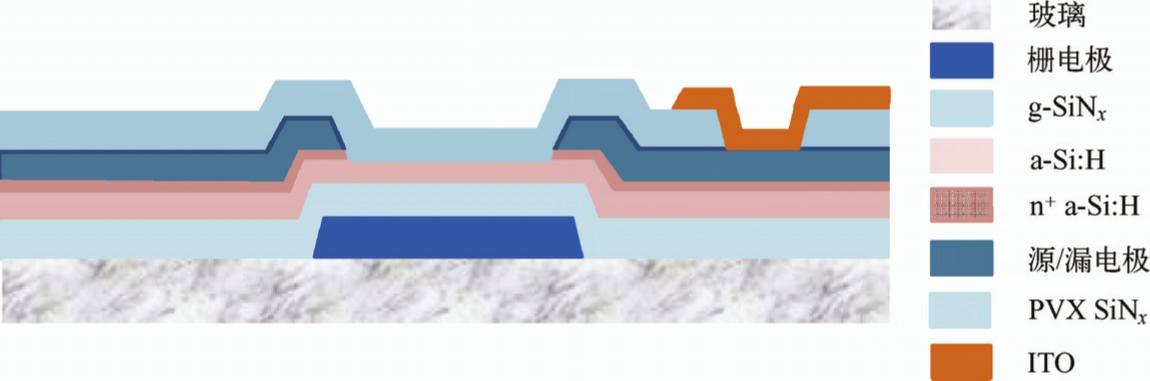

根据制作工艺的差异,底栅结构一般分为背沟道刻蚀型结构(Back-channel Etchant,BCE)和刻蚀阻挡层型结构(Etched-stopper Layer,ESL,或Insulated-stopper Layer,ISL),分别如图2.13和图2.14所示。两种结构相比,背沟道刻蚀结构的制程工艺步骤更少,即其制作成本更低廉,而刻蚀阻挡层结构在制程工艺上不会对半导体层的背沟道造成刻蚀损伤,即其电学特性要更优异。目前,面板厂都广泛采用了背沟道刻蚀结构,一方面是其电学特性能满足显示器的要求,另外得益于设计和工艺技术的提升。一般来说,除非背沟道刻蚀结构不能满足工艺制程的要求,否则在面板制造业内激烈的竞争环境中任何面板厂都不会采用刻蚀阻挡层结构。

图2.13 背沟道刻蚀型TFT结构

图2.14 刻蚀阻挡层型TFT结构

1.背沟道刻蚀型结构

在图2.13所示的BCE a-Si:H TFT剖面示意图中,因为硅岛形成后要用干法或湿法刻蚀硅岛沟道区的欧姆接触层 n + a-Si:H,因此不可避免地也会刻蚀掉一定厚度的a-Si:H层,所以相比ESL a-Si:H TFT的阵列制作工艺流程,它需要更厚的本征a-Si:H层,才能在刻蚀n + a-Si:H层时即使刻蚀了部分a-Si:H层后也还留有足够的厚度。

2.刻蚀阻挡层型结构

在图2.14所示的ESL a-Si:H TFT剖面示意图中可以看出ESL a-Si:H TFT结构的优点就是a-Si:H层上面有一层SiN x 保护着,其沟道区没有像BCE结构那样会受到刻蚀工艺的损伤,因此,a-Si:H层可以淀积得更薄,其电学特性也更优异,但是ESL a-Si:H TFT结构的缺点是制作工艺更复杂,成本也更高。

在BCE a-Si:H TFT结构中,g-Si:H/a-Si:H/n + a-Si:H三层薄膜是在一个多腔室等离子体增强化学气相沉积(PECVD)中一次连续淀积完成。而在ESL a-Si:H TFT结构中,第一次在PECVD中连续淀积SiN x /a-Si:H/SiN x 三层薄膜,然后通过光刻工艺制作出硅岛后,需要再次在PECVD中再淀积n + a-Si:H层。尽管ESL a-Si:H TFT的制作工艺更复杂,相比BCE a-Si:H TFT具有更佳的 I-V 特性,它更薄的有源层厚度既有利于降低源/漏电极与沟道的串联接触电阻,又可以降低光生载流子,即更薄的有源层厚度,吸收光子能力更弱,光生载流子也就更低。

除了常见的BCE结构和ESL结构外,还有半自对准结构(Half-self-aligned)和全自对准结构(Completely-self-aligned)。半自对准和全自对准结构都是ESL结构。自对准结构的一个主要优点就是栅极与源/漏电极之间的交叠电容下降了,因此与该交叠电容相关的像素馈入电压(Feed-through Voltage,Δ V p )也下降了,有利于画面显示品质的提高。但是,在完全自对准结构中,如果栅极和源漏极之间的交叠为零或反而有一定的间隔的话,则由于a-Si:H电阻率非常高(>10 10 Ω·cm),无重叠区将会导致载流子注入困难,即沟道的源/漏接触的串联电阻非常大,引起 TFT 电学性能的大大降低;同时,金属图形的栅极又不能充分遮挡住沟道,引起关态漏电流大大增加。

2.5.2 顶栅结构

图2.12显示的顶栅a-Si:H TFT剖面示意图中,第一次PECVD工艺仅沉积完成n + a-Si:H薄膜,然后再进行第二次PECVD工艺,沉积完成a-Si:H和SiN x 薄膜。两次工艺不能连续进行,使n + a-Si:H薄膜暴露于大气中,导致其氧化而影响了源/漏电极的串联接触电阻特性。这种结构,如果用于液晶显示器中,存在一个致命的弱点就是硅岛直接受到背光源的照射。而在反射式的电泳显示器中,图像显示的光源来自环境光,而顶栅结构的金属栅电极覆盖在硅岛的上面对环境光起到了很好的遮蔽作用,降低了光生载流子,使电泳显示在页面显示中,即使画面不重复刷新,像素电容中的电荷也能长时间保持。

2.5.3 器件基本特性

氢化非晶硅薄膜晶体管的电学特性基本上与金属氧化物半导体场效应晶体管(Metal Oxide-Semiconductor Field-effect Transistor,MOSFET)的相似,应用逐次沟道近似的原理可以推导出薄膜晶体管的两个工作区,即线性区和饱和区。此外,再细分薄膜晶体管的电流-电压特性( I-V 特性),除了这两个工作区外,还有亚阈值区和截止区。当薄膜晶体管工作于线性区时,此时 V ds « V gs − V th ,通过沟道的漏电流就像欧姆定律一样随着施加的漏极电压呈线性关系,即沟道电阻保持不变;当薄膜晶体管工作于饱和区时,此时 V ds > V gs − V th ,通过沟道的漏电流随着漏极电压的增加而基本保持不变。

1.线性区

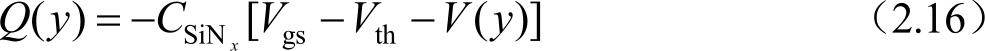

对薄膜晶体管的沟道应用逐次沟道近似(Gradual Channel Approximation)原理,假设沿着垂直于沟道的方向为 x 轴,平行于沟道的方向为 y 轴,如图2.15所示。由栅电极电场感应的载流子的单位面积密度在 y 轴方向是个变量,其值取决于施加在漏极上的电压 V ds 的变化。在 y 轴方向,漏极施加的电压为 V ds ,到源极后电压为零,即沟道中沿着 y 轴的电压可以设定为 y 坐标的函数 V ( y )。

图2.15 逐次沟道近似的TFT沟道剖面示意图

栅极电压逐渐增加,当其大于阈值电压( V th )后,沟道中形成的反型层载流子电荷量 Q 与栅极电压 V gs 的关系为

式中, C SiN x 是栅电极与反型层导电层之间(介质层为g-SiN x :H)的单位面积电容,并且假设沟道中的电势为零。实际沟道中的电压为 V ( y ),因此载流子电荷量 Q 也是 y 的函数,即式(2.15)可以表达为

沟道中的电流可以表达为

式中, W 是沟道宽度; μ n 是电子迁移率; E y 是在 y 处的电场。把 E y =−d V /d y 和式(2.16)代入式(2.17)中,得到

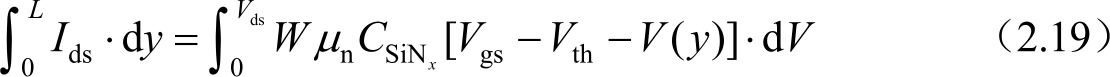

式中,微分量d y 从0到 L (沟道长度)变化,对应的电压 V ( y )从0到 V ds 之间变化,即

得到逐次沟道近似原理的漏电流表达式:

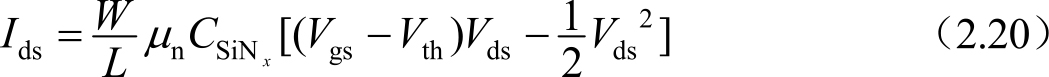

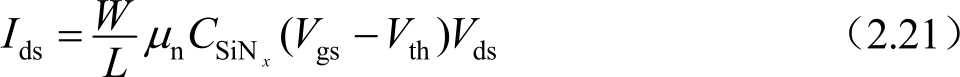

在线性区,因为 V ds « V gs ,所以漏电流可以近似表达为

通过上式,也可以计算出线性区的场效应迁移率 μ n 。

2.饱和区

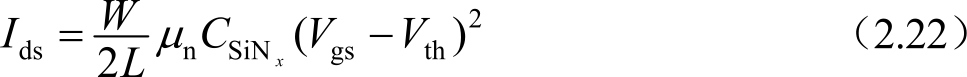

随着漏极电压的进一步增加,栅极电场诱导产生的载流子密度在漏极区被耗尽而逐渐减小到零。当 V ds = V gs − V th 时,反型层的电子沟道被完全夹断(Pinched Off),此时的漏电流达到饱和,即TFT工作于饱和区。当 V ds > V gs − V th ,式(2.21)不再成立。把边界值 V ds = V gs − V th 代入式(2.7)得到饱和区的漏电流,即

通过上式,可以得到饱和区的场效应迁移率。

3.亚阈值区

亚阈值区是TFT从关态到开态的一个过渡区,即电流从低的关态电流(约几pA)以指数形式升到高的开态电流(约几 μA)的区域。在这个区里,随着栅压的变化,费米能级在禁带中移动,因此,大多数感应出的载流子进入到a-Si:H层的深局域态和a-Si:H/绝缘层界面的界面态中。因此,亚阈值区的 I-V 特性严重地受各层膜的质量,比如栅绝缘层、a-Si:H 层和钝化绝缘层的影响。亚阈值区分为亚阈值前区和亚阈值后区。

(1)亚阈值前区

在亚阈值前区(0< V gs < V th ),费米能级位于禁带中部接近本征费米能级的位置。在这个区,漏电流受界面态中陷阱浓度分布和a-Si:H禁带中深能级的类受主局域态的影响,正极性栅极电场感应出的大部分电子都被这些a-Si:H/绝缘层界面态和局域态所俘获,导带中只有一小部分电子能参与导电形成很小的亚阈值电流。因此,在这个区的漏电流非常小,大约为10 -12 ~10 -8 A。当栅极的正极性电压逐渐增加时,反型层的电子密度也增加,漏电流呈指数形式增加。随着栅压降低并转向负压,漏电流迅速降低。有报道对于不同厚度的a-Si:H有源层,亚阈值电流特性有巨大的变化,主要是薄的a-Si:H 有源层(厚度小于80nm)导致导电途径从前沟道转移到了背沟道,即背沟道漏电极受背沟道界面和PVX层的影响。

(2)亚阈值后区

当栅极电压介于亚阈值后区阈值电压( V TR )和0V之间时,即 V TR < V gs <0,称为 TFT 工作于亚阈值后区。在这个区,负极性的栅极电压使沟道界面积累的电子大部分被排斥而耗尽,由于背沟道界面存在较高的界面态密度,在背沟道界面处有一个弱的电子沟道存在,形成了亚阈值后区的导电沟道。栅极电压往负极性方向增加,背沟道界面电荷弱电子数量降到零(继续增加将转变为空穴),亚阈值电流下降,最后过渡到截止区(Poole-Frenkel,发散区)。

4.截止区

当 V TR > V gs 时,TFT 工作于截止区。在这个区的漏电流主要是由于Poole-Fenkel 效应引起的载流子发散而产生的,因此该区又被称为 Poole-Fenkel发散区。随着栅极电压往负极性方向增加,沟道界面处空穴引起漏电流呈指数形式增加,栅极电场增强也使得深缺陷态中的载流子发散而产生。沟道界面处空穴的产生是栅-源交叠区的Poole-Frenkel发散的结果。此时,漏电流是影响TFT LCD的关屏噪声的主要因数。